本篇以e200Z3内核,MPC5634微处理器为例,说明PowerPC的MMU机制,并举以实力说明如何配置使用MMU。

e200Z3内存管理单元遵循32位PowerPC Book E的执行方针。e200Z3处理器的MMU特性如下:32位有效地址被转化成32位实际地址(使用41位虚拟地址过渡);16-entry,完全相连的对应查找表(TLB1),支持9个页(4K,16K,64K,256K,1M,4M,16M,64M,256M);一个32位的PID寄存器(PID0)支持多达255个转换ID;没有页表格式定义,软件可以自由定义页表格式;硬件加快TLB缺失异常处理;通过tlbre, tlbwe , tlbsx, tlbsync, tlbivax 指令和6个MMU寄存器来管理TLB1;IPROT位防止无效,保护关键入口。

首先介绍几个重要的概念。

Effective address有效地址(逻辑地址):代码中使用,当处理器内核取指令或者存取数据的时候,都会提供一个有效地址(或者称为逻辑地址)这个地址是可执行代码在编译的时候由链接器生成的。

Virtual address虚拟地址:虚拟地址在页转换中使用,为中间地址,有效地址转成虚拟地址后再转成物理地址。

Real address实际地址(Physical address物理地址):地址总线上使用的实际地址。

MMU将有效地址映射成对应的物理地址,以访问指令和数据。为了加快MMU规则匹配的处理过程,有效地址和实际物理地址的对应表通常保存在一块单独的高速缓存中,称为对应查找表(Translation Lookaside Buffer,TLB)。TLB可以包含很多个表项(entry),MPC5634的MMU模块包含16个TLB表项。

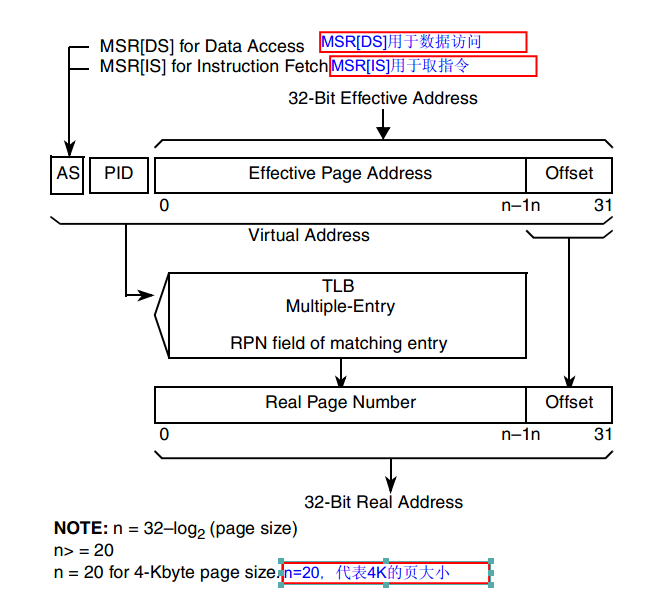

MPC5634的MMU将32位的有效地址映射成用于实际存储器读写的32位物理地址。为了产生这32位物理地址,有效地址首先被分成了页地址(effective page address)和页内偏址(offset)。页内偏址的位数由页面大小确定(log2pagesize),剩余的位数就是页地址。

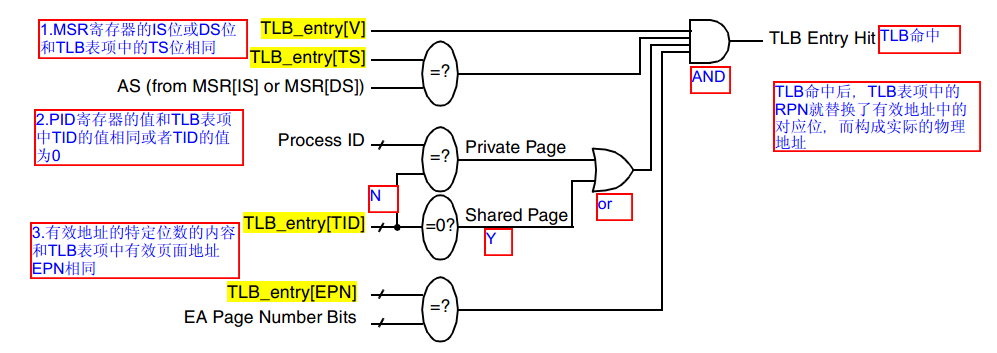

MMU实际上仅对有效地址和物理地址的页地址部分进行映射,页内偏址部分是完全相同的。有效地址的页地址都和所有TLB表项指定的有效映射地址相比较,并使用命中的TLB表项所保存的物理页地址进行映射,得到实际的物理地址。下图描述了有效TLB命中的逻辑处理:

MMU模块有以下寄存器:

PID0(Process ID Register):Book E架构规定每一个有效地址都要有一个PID值与之相关联,PID值用于存储访问的虚拟地址。Book E规定PID寄存器保持当前处理的PID值,PID号由MMUCFG[NPIDS]指出。 PID寄存器是32位的,但是对于e200Z3MMU,只用PID8位。

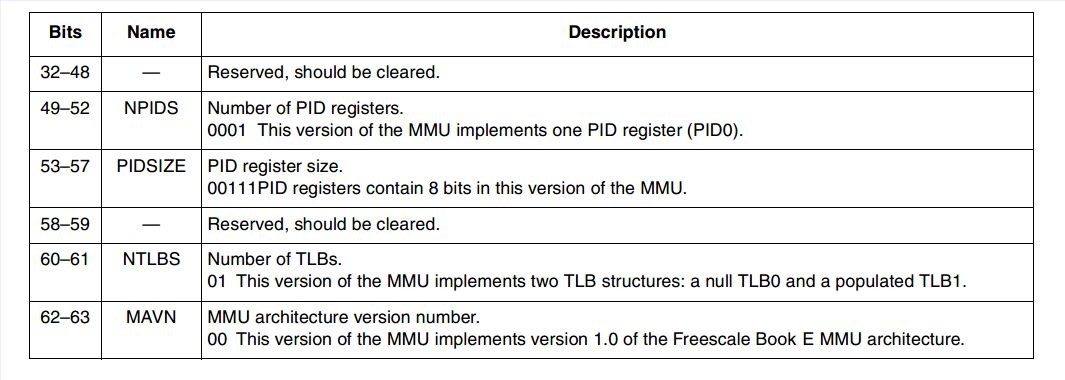

MMUCFG(MMU Configuration Register):32位只读寄存器

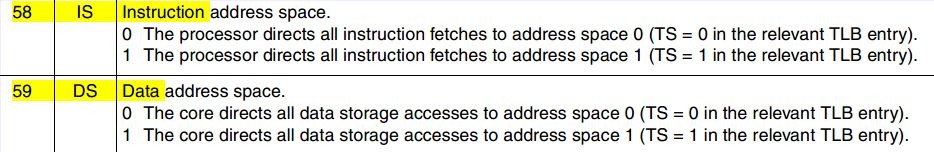

MSR(Machine State Register):

MAS0-MAS4,MAS6(MMU Assist Registers)

e200Z3使用6个MAS寄存器(MAS0-MAS4,MAS6),来对TLB进行读,写和查找。MAS寄存器可以通过mfspr和mtspr两个指令来读和写。

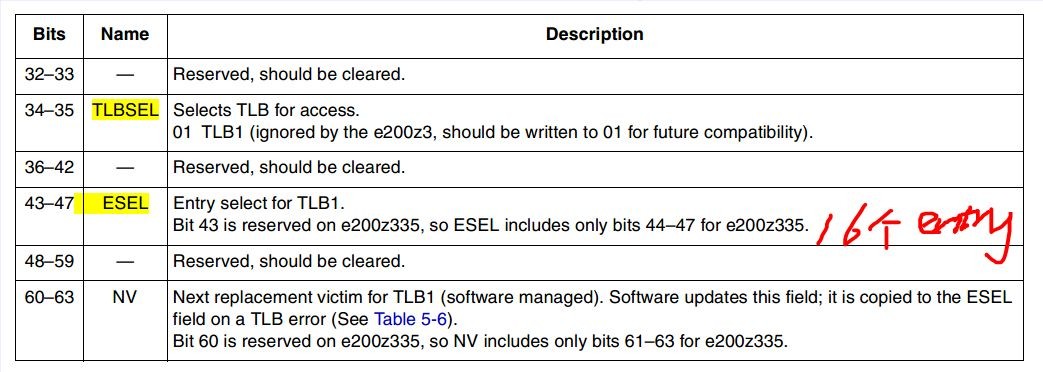

MAS0:

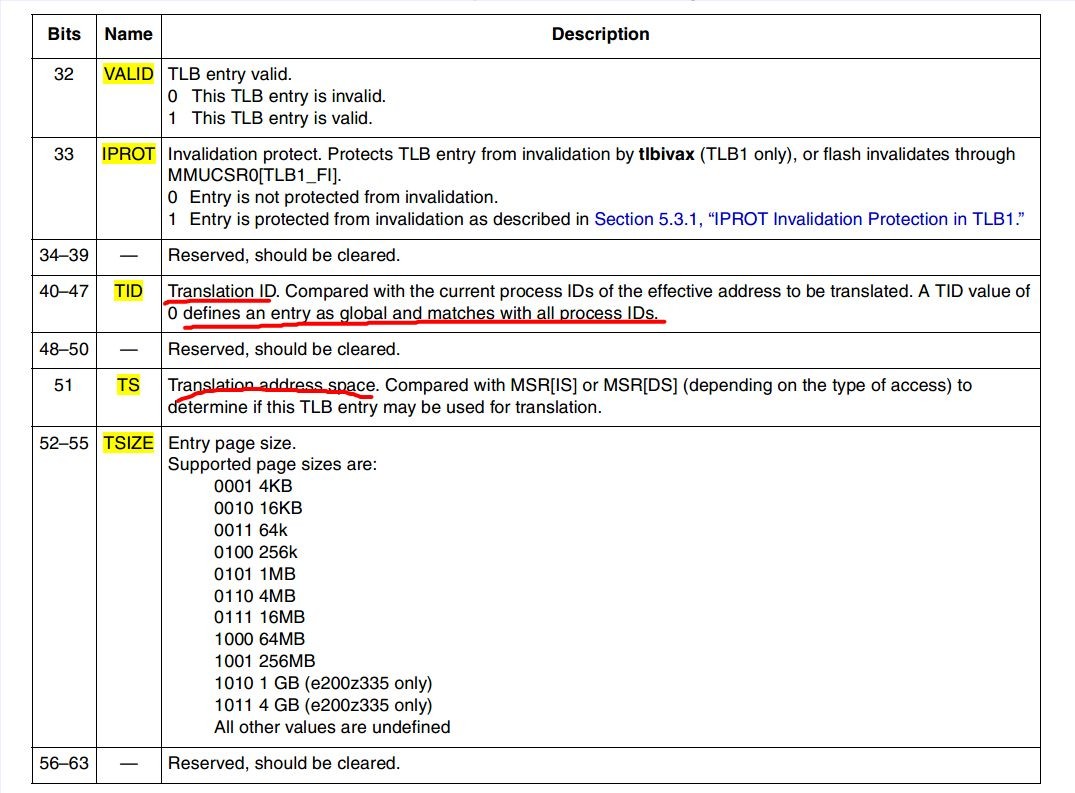

MAS1:

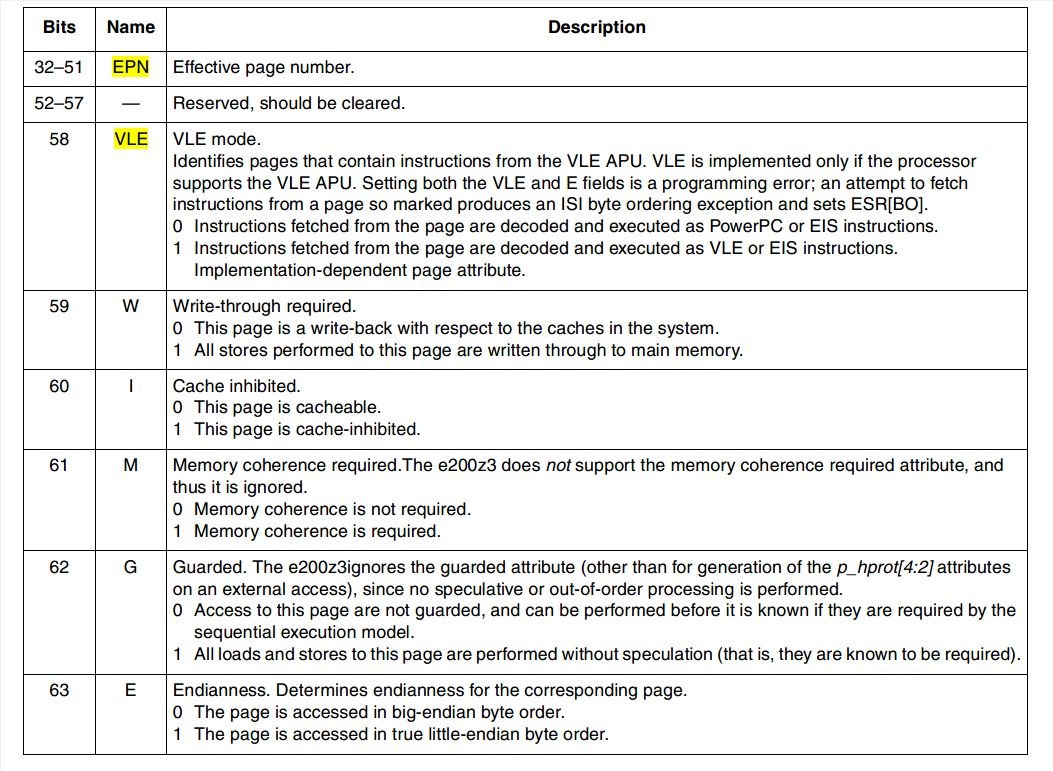

MAS2:

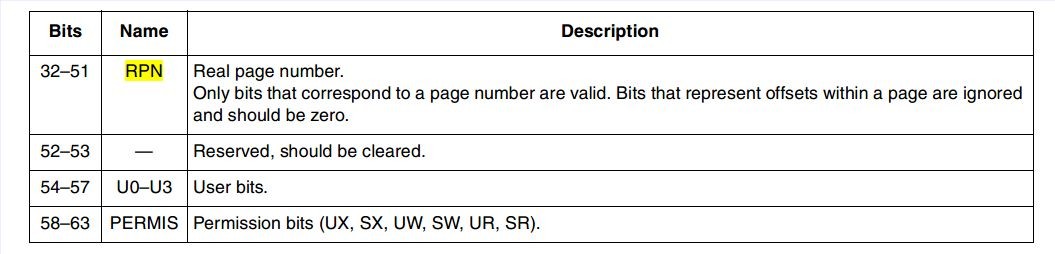

MAS3:

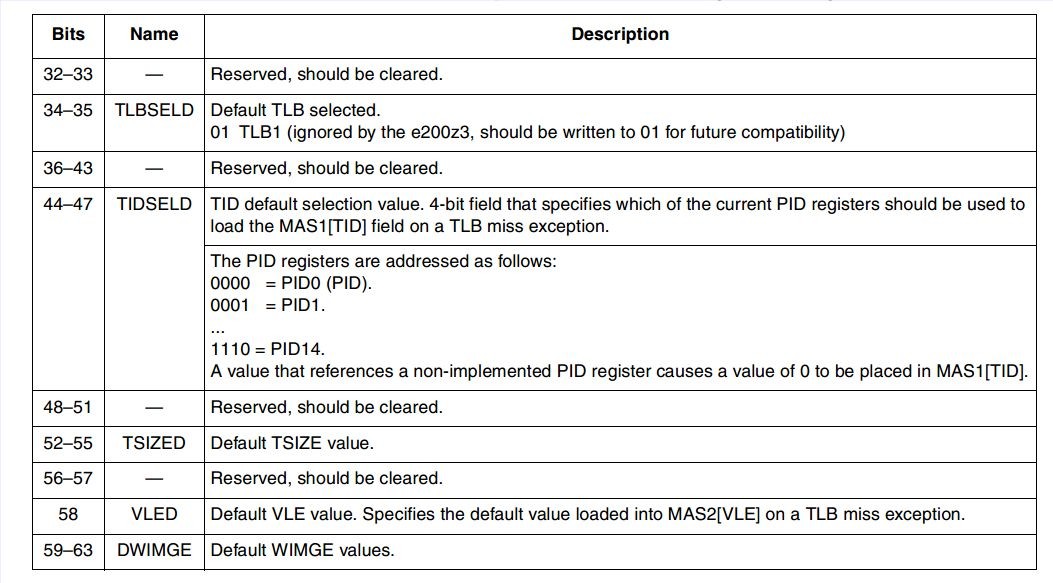

MAS4:

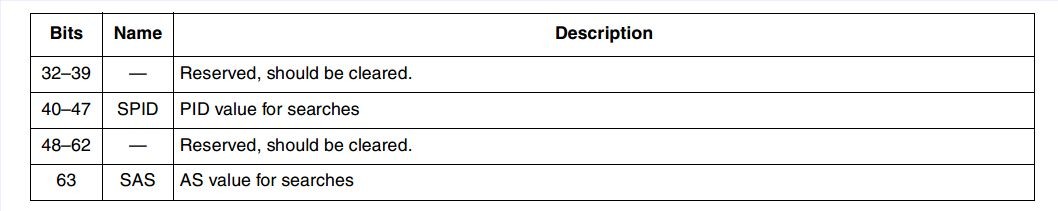

MAS6:

本篇主要是介绍了MMU的概念、原理和相关寄存器,下篇我们以MPC5634微处理器为例来看一下MMU的具体实现。