首先先来说下晶体和晶振这两个概念:

晶体,Crystal,简写为XTAL,双端输出,无方向,没供电。

晶振,Crystal Oscillator,简写为XO,单端输出,有方向,有供电。

两个脚的一定是晶体,4个脚的可能是晶体也可能是晶振

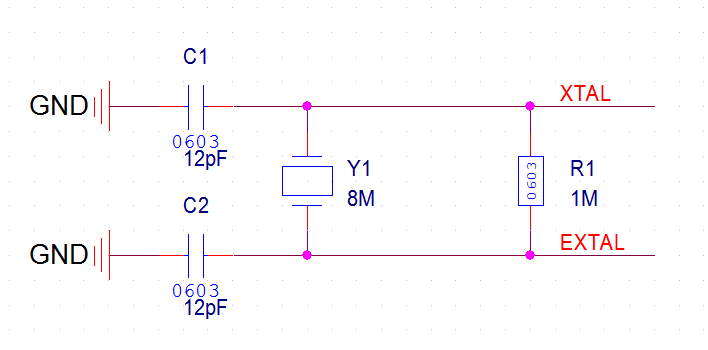

下面看下晶体和晶振的区别

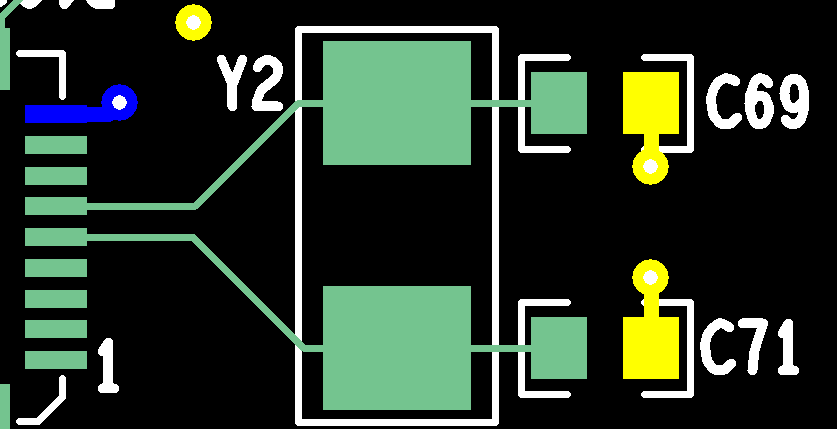

Y1为晶体

Y2为晶振

布局原则

布局紧凑,优先布局在Top层,尽量靠近相关IC

为了减小寄生电容,放置两个电容时,分支长度尽量小

晶振电源采用π型滤波,先大后小

布线原则

布线布同层,尽量不打孔,如果需要打孔,打孔附近必须有回流地过孔或0.01uF的电容滤波

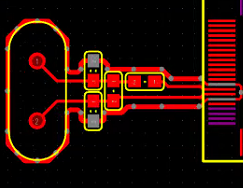

晶体的输出时钟信号线加粗,一般为8或10mil

晶体两根信号线走成类差分形式,尽量等长

为了减小寄生电容,电容的地线扇出的线宽要加粗

对时钟信号线进行包地处理

不允许有Stub线

晶体晶振区域内不允许有其他的信号走线经过

晶体晶振附近应打屏蔽地过孔

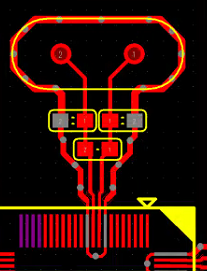

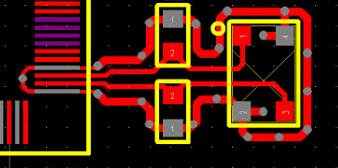

以下几个截图为晶振晶体的PCB布线图:

以上几种布线方式我认为是都可以的,可能大家常见的有争议的几点如下:

1、晶体的起震电容放在内侧还是外侧

2、晶体和晶振外面是否需要铺铜或者包地

3、晶体和晶振下方是否不能走线

晶体的起震电容放在内侧还是外侧

按照理论来说,晶体和电容越靠近IC越好,只要是靠近放置的,电容放在内侧和放在外侧,是不影响晶振正常工作的。但要是距离比较远,建议放在内侧,但也不能保证晶振能正常工作,所以晶振还是要就近放置,优先摆放晶振,才是解决这个问题的最好方法。

晶体和晶振外面是否需要铺铜或者包地

首先说下铺铜和包地的做法,如果做法有问题,那效果还不如不做。

铺铜一般就是在晶振或晶体的外围表层铺地,不与同层其他的地相连,然后需要在晶振或晶体的周围打地孔,使表层的地平面与中间层的地平面相连。

包地就是用线沿着晶振走一圈,间隔一段距离就打孔,把晶振部分电路围起来。

我个人的习惯是不铺铜和包地,原因有如下几个:

1、晶振的频率不高

2、晶振周围比较空,距离其他的线比较远

3、包地和铺铜都需要去修整,比较麻烦,而且做不好的话,还不如不做效果好

其实晶振和晶体可以做包地处理,也可以不做处理。因为做了包地处理的,那晶振和晶体周围就已经有很大的空间是没有走线或者器件的了,本身对外干扰和被外界干扰的程度就很小了,所以做不做包地,差别不会差太多。

如果晶振和晶体周围很近的地方有容易受干扰的线或干扰大的线,首先要做的是拉大间距,然后可以考虑去包地,但注意一定要打好地孔,不然包地部分会成为新加的干扰源,这样就还不如不包地了。

晶体和晶振下方是否不能走线

这个问题有几个争论点:

1、晶振同层下方走线

2、晶振下面其他层走线

3、晶振下面所有层都不能有铜

晶振同层下方走线

这个基本是不建议走线的,晶振自己的线也不建议从晶振同层下方走,其他的线就更不能在同层穿晶振走了。

晶振下面其他层走线

一般会在晶振或晶体的临层铺地平面,如果有地平面隔离,那么从晶振的隔层开始就可以走线了,基本上 不会受什么影响。注意如果走线的话也是走直线,尽量不要有拐弯,一定要避免U型和环路的走法。

晶振下面所有层都不能有铜

这种说法主要是考虑到干扰的问题,没有线从晶振或晶体下方穿过,避免了晶振对外的干扰,也避免了其他的线对晶振的干扰。

那为什么连铺地都不可以呢,这个应该就是考虑到了晶振频率的温度特性。

因为如果晶振的温度过高,会产生频偏,晶振或晶体输出的频率会有一定的变化,要是系统对这个晶振的要求比较高的话,这个影响就会比较大。为了防止温度从地平面传过来,所以晶振和晶体的下方就都不能有铜。

以上对晶振和晶体的布局布线进行了详细的解析,各位可以根据自己遇到的实际项目去判断采用哪种方式去做。晶振和晶体的频率越低,布局布线对系统的影响就越弱。晶振和晶体的频率越高,周围敏感信号越多,距离发热的器件越近,那还是需要认真的去处理一下晶振的走线和周围的信号的。